为了推动RISC-V技术的落地与演进,国家集成电路设计深圳产业化基地携手思尔芯,于2024年6月18日下午成功举办了“数字EDA赋能RISC-V落地演进技术研讨会”。

研讨会由思尔芯产品经理梁琪主讲,主题为《数字异构验证方案应对数字电路设计的新挑战》。梁琪介绍了当前数字芯片设计中的挑战,特别是RISC-V架构的碎片化特征。她指出,这种特征不仅增加了设计的复杂性,也使得验证变得更加困难。如何在确保定制化的RISC-V核心满足设计规范、性能要求,以及处理器性能、功耗和安全性方面的严格验证的同时,又要帮助芯片厂商快速响应市场变化,缩短产品开发周期,并及时推出新一代产品,是当前面临的主要挑战。

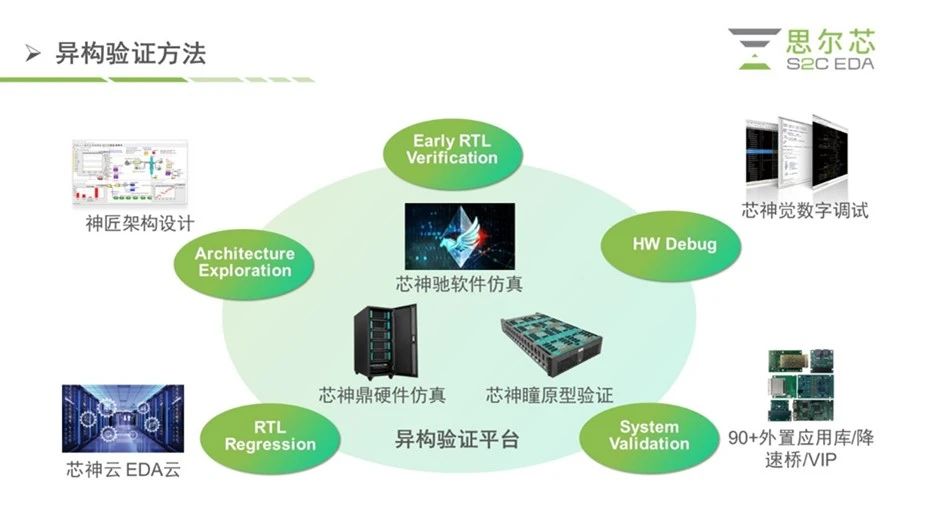

为应对这些挑战,思尔芯提出了异构验证方法。这种方法旨在解决芯片开发过程中每个阶段不同的设计和验证需求,确保设计的准确性。梁琪强调,芯片开发需要充分的仿真和验证,以避免流片失败导致的高额成本损失和市场机会的错失。

通过异构验证,思尔芯整合了多种EDA工具,包括架构设计(Genesis芯神匠)、软件仿真(PegaSim芯神驰)、硬件仿真(OmniArk芯神鼎)、原型验证(Prodigy芯神瞳)和数字调试(Clarity芯神觉),并支持全面上云。这种方法不仅促进了跨团队的高效协作,还确保每个环节的设计都能达到预定的准确性,从而在短时间内高效实现“确保芯片设计正确”的目标。

在接下来的环节中,梁琪又详细阐述了原型验证如何助力RISC-V开发,并通过“香山”Demo进行演示。梁琪解释了选择“香山”进行演示的原因:“‘香山’项目不仅是RISC-V架构芯片设计的前沿,也是我们在该领域技术创新的代表。通过这个案例,我们展示了原型验证如何在实际项目中提升开发效率和可靠性。”

她进一步详细介绍了原型验证在芯片设计过程中的核心作用,特别是对于基于RISC-V架构的设计,原型验证不仅能够显著降低开发风险并加速产品上市,还提供了一个可以在真实硬件上测试软件功能和性能的平台,使“香山”的软硬件工程师能够并行工作,显著加速进程。

在最后的问答环节中,与会者踊跃提问,梁琪耐心解答了关于数字EDA和RISC-V的各种疑问,现场气氛热烈。一位来自芯片设计公司的工程师表示:“梁经理的讲解非常详细,让我们对数字EDA和RISC-V有了更深刻的理解。特别是异构验证方法和原型验证的实际应用案例,对我们的日常工作非常有帮助。”

本次研讨会不仅为与会者提供了深入了解数字EDA与RISC-V技术的机会,还为业界同仁搭建了一个交流与合作的平台。通过此次活动,进一步推动了RISC-V技术在实际应用中的落地与发展,为相关领域的创新和进步注入了新的动力。

思尔芯是国内首家数字EDA供应商,已提供完善的数字前端EDA全流程,也是业内最早开发原型验证工具的企业,客户数量已超过600家。国家集成电路设计深圳产业化基地和思尔芯的此次合作,代表了双方在技术创新和市场应用方面的紧密结合。他们也表示,未来将继续致力于推动RISC-V技术的发展,组织更多类似的活动,促进技术交流与合作,共同迎接技术创新的美好未来。

欲了解思尔芯更多信息,请点击:https://www.s2ceda.com