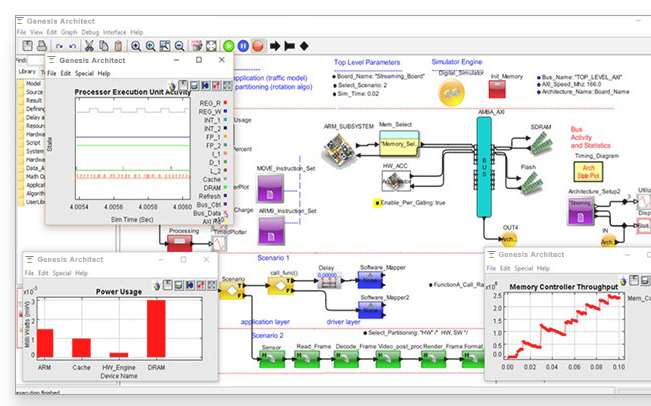

芯神匠的架构设计工具提供了一个图形化和层次化的建模环境,具有开放的DTD XML数据库、多域仿真以及与第三方工具、语言和模拟器的接口。提供了大量建模组件、技术IP模块和工具,用于开发完全定制的组件/子系统。用户就可以灵活地借助模块库中的技术IP和自己定制的IP,在短时间内、在统一的图形化界面中快速实现对系统、子系统、元件或嵌入式软件的行为和性能建模,构造出复杂的系统架构模型。

图形化操作,可以在设计界面直接配置元件参数并将结果可视化

操作界面由四个模型构建选项组成:框图,有限状态机,脚本编辑器和编程,用户可以灵活地选择实现方式

ESL设计的输出是一个可以执行的、具有多个抽象层次的系统级模型。该模型的重要作用是验证目前的设计方案是否满足初始设计规格

通过芯神匠可构建最多具有 300 个层次的模型,还可以通过网络与所有的使用者共享所有模型

支持多种建模方法。用户可以选择适合其探索和应用的一个。使用的方法示例包括Y图、用例到架构映射、网络流建模和软硬件划分

允许用户自定义故障模式,随机插入软硬件、网络、RTOS、功耗等故障或故障组合后自动进行功能安全分析,产生通过ISO26262认证的报表,加速用户取得功能安全认证

通过技术IP模块库进行快速构建模型,使用适当的计算模型进行模拟,并自动生成报告进行分析

为了支持准确建模,框图编辑器具有错误检测和报告、语法检查器、图形调试器、跟踪和日志记录

提供 500 多个用户配置报告,包括延迟,吞吐量,利用率,缓冲区占用,退出/进入数,功耗,峰值功率,功率/设备,功率/任务,累积功率,命中率,失速时间和服务质量

支持与第三方工具、语言和模拟器的接口。包括与硬件,工具和FPGA板的跟踪文件,文本文件导入/导出的XML接口,允许用户自己开发定制组件或者导入已有的C/C++/Java/SystemC/ System Verilog/Verilog/VHDL模块

提供以太网线缆从软件到FPGA板的千兆以太网链接套件,从而实现软件与FPGA板的协同仿真。用户还可以将用SystemC/TLM/Verilog/VHDL语言开发 的IP核封装成块,导入到模块库中,方便后续系统架构使用

Genesis Architect 使用者界面