思尔芯作为国内首家数字EDA供应商,在数字前端验证领域拥有深厚的技术积累和丰富的产品线。其数字前端EDA全流程解决方案涵盖了架构设计、软件仿真、硬件仿真、原型验证、数字调试等多个环节。

在ICCAD2025思尔芯介绍公司原型验证领域的相关进展和新产品硬件仿真芯神鼎 OmniDrive 。

原型验证领域新进展

RISC-V架构在AI芯片领域的布局已呈现全面渗透态势,其开源、灵活、可扩展的特性与AI计算需求高度契合,正从嵌入式端侧向云端高性能计算加速拓展,形成多核异构、定制化加速的生态化发展格局。

思尔芯副总裁陈英仁表示,在原型验证领域,对于采用 RISC-V 架构的 AI 芯片而言,必然与软件紧密关联。因此,市场对于高性能的验证方式有着迫切需求,这类验证方式不仅要能助力软件开发,甚至在初创公司募资阶段,也能通过提供Demo向投资方展示产品潜力。此外,思尔芯在硬件仿真赛道推出了新产品。其新品OmniDrive是一款原型验证和硬件仿真双模式产品。

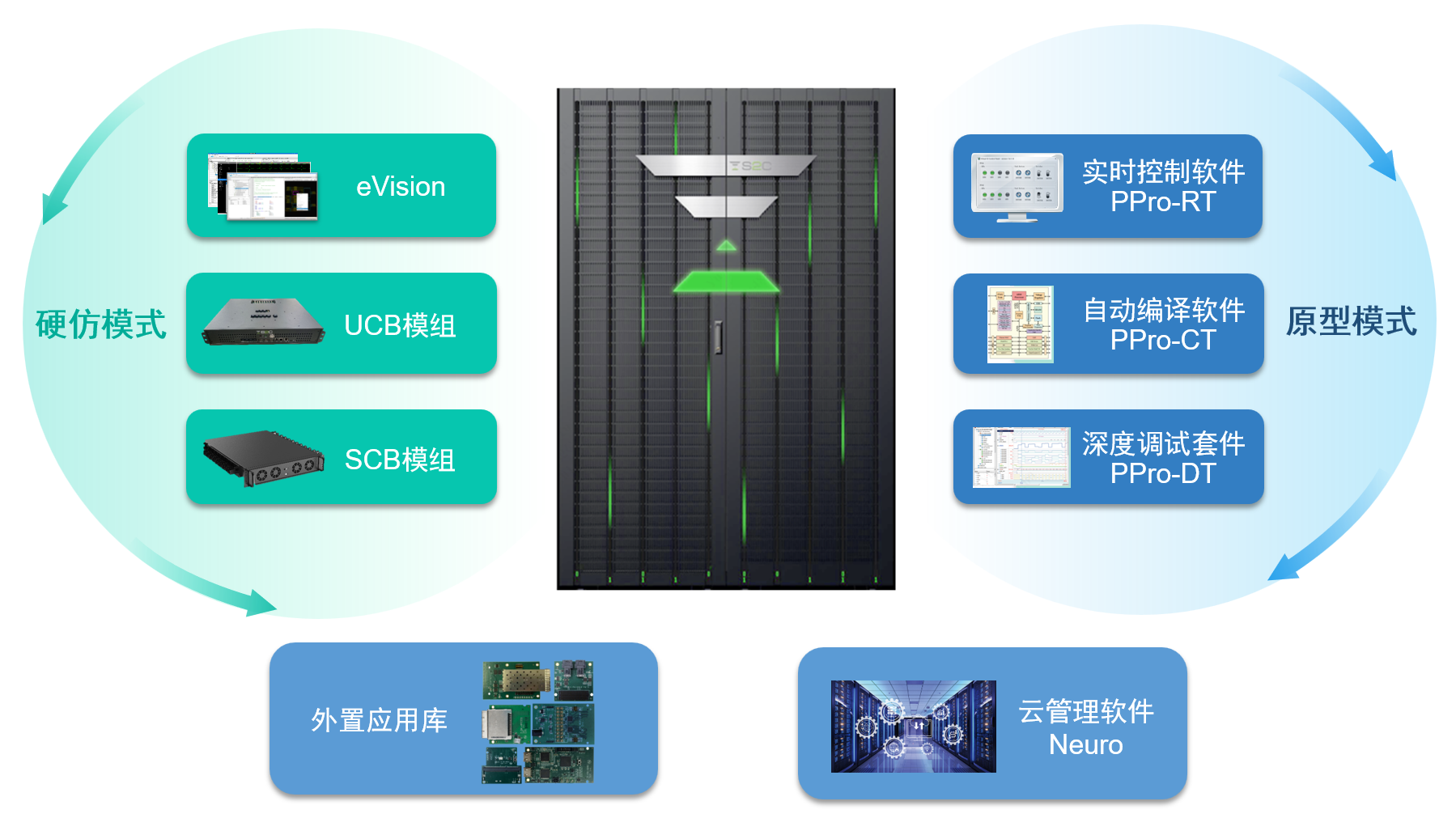

硬件仿真侧重于调试功能,运行速度相对较慢;而原型验证则追求高速运行,但高速运行往往难以配备完善的调试工具。然而,二者底层硬件本质相同。基于此,思尔芯开发了双模式架构,通过同一套底层硬件,搭配不同的软件以及部分硬件配件,即可实现原型验证与硬件仿真两种功能。

陈总表示,对客户而言,只需一次投资,就能实现“一鱼两吃”的效果,这种新架构在资金投入和资源利用方面,为客户提供了更为节省的方案。

陈总补充,从本质上来说,RISC-V和ARM架构都十分契合原型验证的需求。这是由于二者均与处理器以及软件紧密相关,在芯片设计流程中,除了对硬件进行验证外,软件的开发与验证也是关键环节。因此,在原型验证阶段,都期望能够实现高速、高性能的软件验证,以此确保软件与硬件能够良好适配、协同工作。

原型验证此前面临的一大挑战便是大型设计项目。思尔芯最新研发的RCF软件,实现了在RTL层面的分割流程。其优势在于,从项目初始阶段就能对RTL进行切割,进而在生成以及FPGA上的布局布线过程中,能够并行处理多个任务,从而加速整体开发进程,有效解决大型设计项目的难题。有了这项新的分割技术,大型设计项目能够得到更高效的处理,尤其能更好地应对AI领域的大数据需求。

硬件仿真OmniDrive

AI发展是不可逆转的趋势,其应用只会愈发广泛。当下,AI算法不仅持续演进,而且变动幅度相当大,设计复杂度也与日俱增。对我们而言,所提供的硬件仿真与原型验证工具,恰好能很好地满足这一需求。

思尔芯于2022年12月推出首款国产企业级硬件仿真系统OmniArk芯神鼎。如今,又有一款新产品Omni Drive 面世,目前该产品正在客户处进行测试。

OmniDrive该设计基于业界最大容量密度的FPGA打造统一硬件平台,支持硬件仿真与原型验证模式灵活切换;具备丰富仿真验证模式,可满足不同场景需求;拥有全自动编译流程,提供多样编译策略以契合不同编译目标;调试手段高效精准,运行阶段能任意切换Trigger信号实现问题快速定位;采用波形信号过滤技术,显著增加波形存储深度并节约存储资源;支持多用户并行运行,且编译效率高,仿真速度可达数MHz级别。

加强应用层级生态合作

除了在产品层面精益求精、打造卓越品质之外,思尔芯在生态建设方面也投入了大量精力。针对RISC - V,思尔芯前几年就围绕其构建的生态体系,今年已经开花结果。此次ICCAD思尔芯站台上展出了多个RISC-V代表案例:开芯院香山“昆明湖”多核CPU与NOC协同设计验证、晶心科技矢量处理器IP核AX45MPV运行DeepSeek大语言模型等实例。充分体现了思尔芯的技术能力与落地成效。

陈总称,客户的痛点主要在于如何更轻松地入门上手,以及如何缩短验证所需的时间。在与IP合作商的合作中,思尔芯与芯动科技等企业相互依存、相辅相成。这些IP合作商还提供了众多接口,而这些接口厂家也有意愿与我们展开合作。此外,我们还有一些额外产品,例如降速桥等,这类产品在使用过程中需要用到IP,我们便与IP厂商携手合作,共同为客户提供完善的解决方案。

陈总补充,当前的设计领域,主要聚焦于RISC - V设计、GPU设计等几个大类型。我们期望通过积累充足的案例和数据,不仅能够帮助我们的直接客户,还能助力这些IP厂商的客户更快地达成他们所期望的结果,推动整个行业向前发展。

生态系统的建设对于EDA公司而言至关重要,这不仅是技术发展的支撑,更是其实现市场竞争力与持续创新的核心驱动力。2025年,思尔芯在这一战略方向上进一步深化,着力加强应用层级的生态合作。公司通过精准定位行业合作伙伴,建立起更加紧密与协同的合作关系。