(转自芯思想微信公众号)

思尔芯S2C,致力于数字前端设计验证解2、验证贯穿整个芯片设计流程决方案,2004年孵化于座落在北京东路668号科技京城的上海集成电路技术与产业促进中心(ICC),2018年进入国微集团EDA大家族,共同承担并完成国家数字EDA全流程的重大专项,开启国产EDA研发新篇章。

S2C的内涵1=Silicon valley to China(硅谷到中国)

S2C的内涵2=System to Chip(系统到芯片)

思尔芯的“第一”

中国第一家数字EDA公司

中国第一家出现在DAC现场的公司

验证的重要性[1]

芯片设计被誉为人类历史上最细微也是最宏大的工程,芯片研发工作者需要把数百亿颗晶体管集成在面积最小至指甲大小的芯片上。如此复杂的工程,从设计阶段开始就错综复杂,很多环节互相串联,形成一个长流程,需要专业细分、领域不同的研发人员、专业人士和科学家集团队力量协作而成并且保证每个环节的高正确度。这样精密的研发和跨领域协作是完全不可能靠手工完成的,研究人员所仰赖的是一种名叫EDA的工具。其全称为电子设计自动化(Electronics Design Automation)工具。正是这一工具在1983年问世,释放了芯片研发者的创造力,把手工设计完全升级为电子自动化的设计,从而促成芯片技术发展进入大爆炸时期。

首先,我们先了解一下验证的重要性。

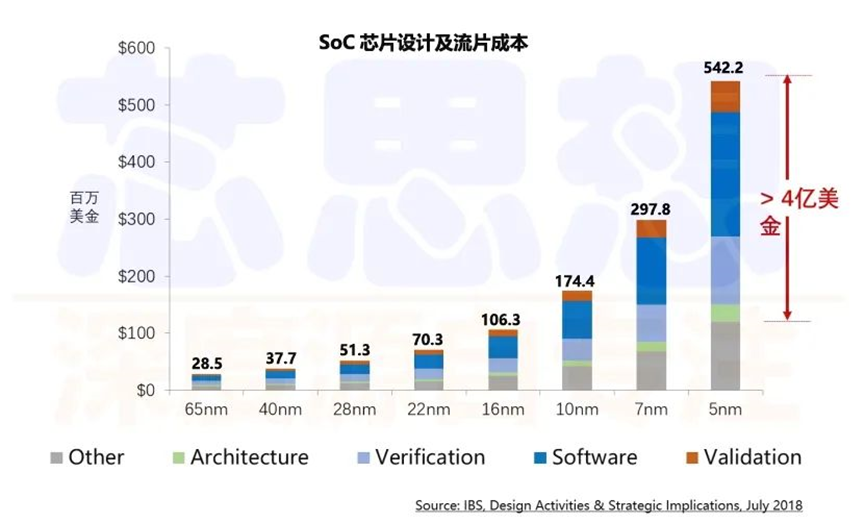

1、芯片进入SoC时代,验证工具变的必不可缺

系统级芯片(SoC- System on Chip)将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,是当前芯片里的主流。SoC这一概念在20世纪90年代出现,经过近30年的发展,SoC可集成的内容越来越多,晶体管数量越来越大、功能越来越多元化,使得设计原理变的异常复杂。毫不夸张的说,一款SoC设计对于一个配置齐全的、有经验的研发团队来说,也需要3-5年的时间才能完成全部研发工作。

高昂至上亿美金的流片(Tape-out)成本,不可逆的研发时间成本,导致芯片设计的每个环节都不容许出现一点点错误;而且随着SoC所继承的内容和复杂程度日益提高,验证需要探索的空间和范围越来越大,每一次验证都像是一次“大海捞针”,因此验证所需要的时间亦越来越长。EDA里的验证工具已然必不可缺,验证越充分,芯片的成功率就越高。

当前的验证几乎必须贯穿芯片设计的每个步骤,以便芯片研发团队及时发现错误,保证所投入的巨大研发成本不会覆水东流或错过最佳上市时间。据悉,在现在的SoC研发项目中,仿真和验证的时间占了整个项目70%以上的时间,而仿真和验证工程师也占了整个团队的70%以上。因为只有经过充分的仿真和验证,找出足够多的bug,才能放心拿去流片。

2、验证贯穿整个芯片设计流程

芯片在设计启动伊始就会设定非常严格的设计周期和面市时间,环节一环扣一环,验证是一个反复和交叉作业的工作内容,贯穿整个芯片研发周期,环节繁复但时间不能有任何延误,从而造成在单位时间内的验证任务成指数增长。并且,验证不仅仅是在芯片设计阶段,即使一款芯片已经量产出货,验证的工作可能依然没有结束。

这张图按照芯片研发的时间进程,示意了验证的每个环节:

(1)产品规划

在研发初期首先要启动的是验证规划,这是为了在产品规划的同时即确定验证方案和技术路线,并且保证验证结果有一定量的调试时间并有可行的调试方案。

SoC研发时非常依赖选用一部分可复用的成熟IP核,以加快其本身的研发速度。但在选择合适的IP核时要同时考虑的因素有很多, 功耗、性能、安全以及成本,还有IP核与IP核,IP核与其他模块之间通讯和数据交互的界面接口,等。因此,在初期,还要为某些标准的模块需要提前准备好验证IP核(Verification IP,VIP)并规划好不同的检测点,并具体落实在各个研发阶段和模块中。

(2)架构定义

SoC设计首先要定义系统的架构,其中包括但不限于定义功能、明确各IP和模块之间的通讯协议、功耗与性能的妥协关系等等。架构定义要基于该芯片使用后所面临经典工作场景进行假设和模拟,所以在架构定义阶段,需完成两个非常重要的验证:

一个是不同通讯协议下的功能验证(Functional Verification),该验证允许设计工程师在设计阶段发现高阶的协议性错误(bug),在设计早期以非常低的成本进行修复。而如果进入到产品阶段才发现,修复的成本将会非常高。

另一个同步进行的是原型验证 (Prototyping),就是把硬件原型模拟化,提前对软件和硬件的配合表现进行验证。这样提前验证的好处是,在芯片制造前,便可以开展软硬件协同设计,提前发现问题、检测问题并解决问题,确保芯片在真正可使用时,研发团队已经拥有一个成熟的软硬件整体方案,芯片能切实支持软件的应用,大大将研发时间提前,提升整体研发效率。

(3)流片前验证

前文提到,SoC设计为了缩短研发周期会采用可复用IP核和新IP。每一个IP核验证都在各自单独的环境中完成,以确保单独IP功能正确;但在复杂的SoC验证链中,不仅需要单点验证,更需要有多种验证手段进行系统性验证,确保各种IP核以及其他模块能协同工作。

IP验证中惯用动态仿真(Dynamic Simulation)和形式化验证(Formal Verification)。二者在使用时都需要基于单独的验证基础环境,前者需要模拟出基础环境;后者要通过数学建模,在数字世界里搭建出环境假设和目标断言。验证工程师通过比较结果、仿真波形比对最终来判定测试用例是否通过。

流片前验证是SoC研发过程中耗费时间和资源最大的验证环节,而且是一个增量的连续过程,随着设计成熟度和设计复杂性的提高而提高。

(4)硬件加速

严格意义上来说,硬件加速(Emulation)的使用是在流片前,属于流片前验证的一部分,但参与过芯片设计的研发者都知道,这个环节是流片前验证和流片后验证的桥梁,它将还处于RTL级别的设计放到一个可重构的虚拟硬件环境中,让验证速度得到成千上万倍提升,同时也让软硬协同成为可能。利用这种技术,我们可以在数小时之内,将操作系统在RTL模块上启动起来。

验证速度的提升,让验证的效率大幅提升,对验证成本的贡献是无可比拟的。俗话说,有得必有失,有失必有得。验证工程师发现,验证速度的提升的同时,能够观察的信号将会急剧减少,并且那些需要被观测的信号,必须在产生FPGA比特流之前就要定义好,一旦没有定义,重新编译可能又需要耗费好几个小时。

为了解决上述问题,现在EDA公司已经推出了硬件加速器(Emulator),硬件加速器在仿真速度和可观测性之间进行权衡和取舍,速度上向原型验证靠拢,而可观测性向仿真器靠拢,在仿真器和原型验证之间增加一个验证产品,但是因为硬件加速器结构特殊,价格昂贵,只有芯片利润相对丰厚的大企业才用得起。

(5)流片后验证

流片后验证一般发生在芯片实际生产结束以后,在芯片进行量产之前,将测试批芯片在实验室进行各种测试,确保功能、时序、性能、功耗、物理应力得都符合设计预期,在完成所有的验证以后,再进行批量生产。如果在这个阶段发现错误,其修复的成本将会非常高昂,甚至成为不可能。如果一个错误被确认为功能错误,设计团队就必须对进行修复,修复错误的方法有多种,包括利用系统微码来避免失效的条件。但如果错误必须在硬件层面进行,那就需要重新流片了。

综上所述,在整个芯片开发过程中,验证就是一场前哨战,是整道防线上成败的关键。在芯片进入流片之前,需要保证其设计完全符合需求规格,解决所有潜在的风险,并修正所有的缺陷。

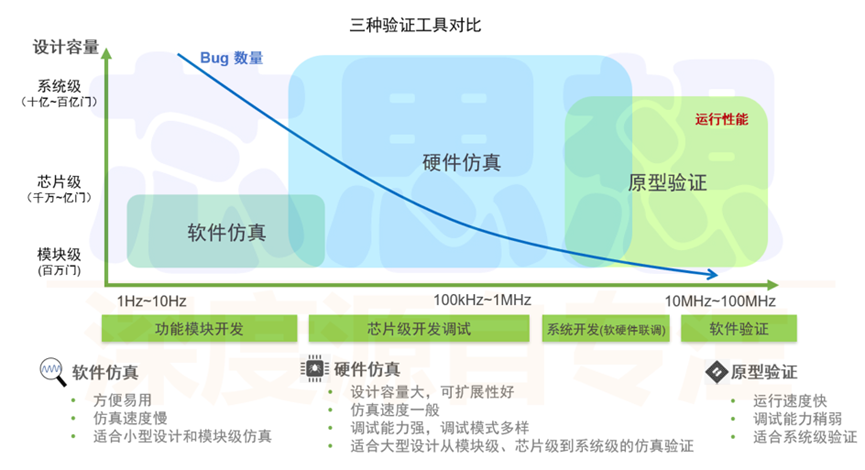

验证工具的种类

战斗已经打响,战斗中的工程师可以使用软件仿真、硬件仿真和原型验证手段进行防守。

1、软件仿真

软件仿真是基于硬件描述语言对数字电路设计进行功能和特性的仿真和验证。它会通过在计算机环境中模拟硬件行为,验证电路设计是否符合原意。仿真过程是正确实现设计的关键环节,它以硬件描述语言(如VHDL或Verilog)编写的模型为基础,检验设计中的功能是否正确无误。

一般来说,软件仿真分为功能仿真、综合后仿真和时序仿真,分别对应于RTL设计输入后、综合完成后、布局布线完成后等步骤。

2、原型验证

原型验证是在早期阶段通过与最终芯片接近的原型硬件来测试和验证电路设计,通过接近最终芯片的运行速度确保设计出正确的芯片。原型验证将设计映射到FPGA阵列,通过模拟芯片的功能和应用环境,来验证芯片整体功能,并提供片上软件开发环境。因为相比硬件仿真,原型验证的运行速度更接近于真实芯片,可以配合软件工程师来进行底层软件的开发。这一流片前的软硬件协同开发,是其最不可替代的地方。

原型验证流程中的关键步骤,包括设计分割、分割后的系统级时序分析、编程和下载、功能验证调试等步骤。

3、硬件仿真

硬件仿真首先将硬件设计(通常以HDL,例如Verilog或VHDL编写)编译,然后加载编译后的设计。在一些系统中,设计可能被加载到专门的硬件中(例如FPGA)。一旦设计被加载,硬件仿真就可以运行设计,并观察其行为。硬件仿真通常会提供观察和调试设计内部状态的工具。最后,工程师可以根据结果分析设计的正确性,查找并解决问题,以优化设计。

从上图可以看出,三种验证工具都有各自的优点,也有各自的不足。工程师会在芯片设计的不同阶段选择不同的验证工具,提高验证效率,加速验证的收敛。

根据芯思想研究院的调研数据,目前验证工具整体市场规模约为30亿美元;随着AI芯片和GPGPU芯片的火爆,预估到2030年,市场规模可能超过50亿美元。

如此庞大的市场,玩家当然不仅仅是新思科技、楷登电子、西门子EDA三巨头,国内近年来也涌现出不少新玩家,包括芯华章、合见工软。但是今天文章的主角是坚守验证工具市场20年的思尔芯。

从点串链,打通验证全流程

2024年1月18日举行的以“思尔合作,芯路共赢”为主题的EDA生态协作发展论坛暨思尔芯20周年成果展现场,林俊雄先生表示,当他站在会场露台上,俯瞰着这座城市,他的视线从历史悠久的豫园扫过,远眺前方林立的现代摩天大楼,包括被誉为“魔都三件套”的东方明珠电视塔、金茂大厦和环球金融中心。这一幕让他回想起二十年前初来上海创业的时光,创业过程中,经历的辛酸和艰难远比表面看到的光鲜要多得多。那时中国的芯片设计业还处于起步阶段,而国产EDA领域还是一片荒芜。林俊雄先生却在这片“荒芜”中看到了中国芯未来。

原型验证的前世今生

林俊雄先生表示,原型验证是一个快速增长且竞争激烈的市场,并提到大规模应用是在2008年新思科技收购Synplicity进入市场以后。

本文简单叙述一下原型验证的前世今生。

1990年代,多伦多大学(University of Toronto)的Transmogrifier-l、北卡州立大学(North Carolina State University)的AnyBoard、斯坦福大学(Stanford University)的Protozone以及加州大学圣克鲁斯分校(University of California,Santa Cruz)的BORG等项目,开始探索如何在小型原型验证板上实现HDL芯片设计。高校项目为后来的商用验证工具探索了多种可能性。

1992年是原型验证的元年。Aptix在1992年推出了名为System Explorer的系统,利用FPGA及自创的互联芯片实现了商用原型验证工具,为芯片验证方法学作出了开创性贡献,因此被业界视为原型验证工具的先驱。尽管Aptix在2005年被收购,成为Mentor的一部分,但Aptix的成功给了产业很大的启示,并激发了更多公司进入这个领域。

1998年Dini Group推出原型验证工具DN250k10,2015年发布了DNVUF4A;2003年瑞典HARDI Electronics AB推出原型验证系统HAPS-10;2003年法国初创企业Taray Inc.推出原型验证工具7Circuits。但这些产品还需要工程师大量的手动搭建原型验证环境。2005年思尔芯在DAC上推出了其首款原型验证产品V2 IP Porter[2]。Dini、HARDI、Taray也都已消失在EDA的并购浪潮中,只有思尔芯依托中国芯土壤,抵住收购诱惑成功坚守。

2008年新思科技(Synopsys)收购Synplicity(Synplicity于2007年收购HARDI),2010年推出HPS-60,容量达1800万个专用集成电路(ASIC)逻辑门。2012年推出了全球首款真正意义上的自动化原型验证产品HAPS-70,可以支持范围广泛的、各种大小的设计,其容量可从1200万到1.44亿个专用集成电路逻辑门;同时将可将原型验证生产力提高10倍。2015年推出了原型验证产品HAPS-80,可支持高达16亿个专用集成电路逻辑门,并支持面向并行设计执行的远程使用和多设计模式;2021年推出最新一代原型验证产品HAPS-100。2019年收购Dini,进一步扩大了公司在原型验证市场的领先地位,并将其FPGA解决方案拓展到网络应用和高频/低延迟算法中。

楷登电子(Cadence)在2010年3月收购Taray之后,依靠Taray的路由感知管脚分配综合技术,才算一支脚迈进了原型验证市场,并和Dini合作开发于2017年推出了第一代FPGA原型验证平台Protium S1,2019年发布第二代Protium X1,2021年推出第三代Protium X2原型验证系统,专注完善原型验证产品和硬件仿真产品之间的衔接流程,实现两者的快速相连。

西门子EDA(前身Mentor Graphics)在1990年代末就从Aptix获得了仿真技术许可,并在2005年完成对Aptix的收购,2015年收购Flexras Technologies SAS获得Wasga自动分割技术,2021年收购PRO DESIGN Electronic旗下的具有FPGA桌面原型验证技术的proFPGA 产品系列,终于成就了公司两类原型验证系统:Veloce Primo企业级FPGA原型验证系统和Veloce proFPGA桌面FPGA原型验证系统。

2021年,芯华章推出原型验证系统桦捷HuaPro P1,基于自主知识产权的全流程软件,可实现设计原型的自动综合、分割、优化、布线和调试,2022年推出的集成原型验证和硬件仿真双模式的桦捷HuaPro P2E,基于统一芯片、统一硬件和统一软件,真正实现了全新的硬件仿真和原型验证双模工作模式[3];2014年华桑电子推出PHINE Design系列原型验证,至今已经推出第四代产品[4];2009年亚科鸿禹推出第二代原型验证产品为VeriTiger,至今已推出第七代产品[5]。

坚守初芯,持续创新

2003年,EDA学术界的大牛、加州大学伯克利分校(UC Berkeley)教授Alberto Sangiovanni-Vincentelli(阿尔伯特·桑乔瓦尼·温琴泰利) 在DAC(设计自动化大会)40周年发表主题演讲《The Tides of EDA》,讲述如何看待40年来DAC相关的研究成果,阐述EDA(电子设计自动化)未来的趋势和挑战,并强调这是一个EDA大变革的年代。

感受到了时代的呼唤,以及大变革的到来,DAC2003结束后不久,林俊雄先生就离开了Aptix并在美国硅谷的核心地区-加利福尼亚的圣何塞创立了思尔芯(S2C),2004年1月迅速在上海建立了总部和第一个研发中心。

从FPGA原型验证先驱公司离职创业的林俊雄,依然选择了自己熟悉的领域。这一大胆的决策预示着新时代的到来。诚如上海市集成电路行业协会秘书长郭奕武先生在EDA生态协作发展论坛暨思尔芯20周年成果展开幕致辞所说,思尔芯作为国内首家数字EDA企业,自2004年成立以来,在上海ICC的孵化下开始了它的芯程。今天,它已经成为上海市的重点EDA企业,并荣获国家级“专精特新”小巨人企业的殊荣。在过去的20年中,思尔芯不仅站在了科技创新的前沿,还以其卓越的EDA技术推动了整个集成电路行业的发展。思尔芯的成长历程不仅见证了中国集成电路产业的自强不息和砥砺前行,也展现了国产EDA坚守初心、勇于突破自我的精神。

图为上海集成电路行业协会的秘书长郭奕武先生

二十年耕耘,思尔芯实现验证工具从点到链的突破!从2005年推出第一代原型验证系统以来,至今已经推出八代产品,客户包括英特尔、三星、索尼、瑞昱、黑芝麻、开芯院等知名芯片公司,是久经市场验证和认可的成熟产品;在2018年进入国微EDA大家庭后,配合国微集团在数字EDA领域的布局,后通过强化核心技术和外部并购,全面布局了包括架构设计(Genesis芯神匠)、软件仿真(PegaSim芯神驰)、硬件仿真(OmniArk芯神鼎)、原型验证(Prodigy芯神瞳)、数字调试(Claryti芯神觉)等数字前端EDA工具,如今已经形成完善的数字前端设计验证解决方案,全方位覆盖数字芯片验证。

国微芯执行总裁兼首席技术官白耿博士表示,通过思尔芯的芯神驰Pegasim软件仿真构建的Testbench平台,和国微芯提供的标准接口,进行数据交换,以实现数模混合仿真。这种协作方式有效地实现了高效的数模混合仿真,不仅展现了两家公司在EDA领域的专业实力,也为处理日益复杂的芯片设计问题提供了新的解决思路。同时PegaSim还可以与国微芯的形式验证工具相连,着重于对覆盖率库文件中那些不可达部分的深入验证,显著增强软件仿真过程中的代码覆盖率。这种形式属性验证的应用可以通过增加激励或优化代码来提高代码覆盖率,并进行覆盖不可达性的检查。它还支持对指定模块或特定代码行进行一种或多种类型的覆盖不可达性检查。这种方法有效地识别和删除无意义或冗余的代码,从而优化了内在逻辑,提高了整体设计的质量和效率。通过这种方式,思尔芯的PegaSim不仅增强了仿真的全面性,还优化了设计过程中的关键步骤。这样的进步确保了更高效和准确的芯片设计,为系统级芯片(SoC)的开发带来了显著的技术优势。

复旦大学微电子学院院长张卫教授在致辞中肯定了在过去20年里思尔芯在行业中的前瞻性作法,还强调了思尔芯在业界的知名度以及取得的成就,包括其芯神系列产品在软硬件方面对芯片设计产业的贡献。

图为复旦大学微电子学院院长张卫院长

合作创新,构建芯生态

复旦大学微电子学院院长张卫教授在致辞中还指出,在政府大力支持下,国产EDA生态初步形成。但目前这一生态还相对脆弱,未来需要更加开放和合作的心态。上海市集成电路行业协会秘书长郭奕武先生也表示,在地缘政治和经济发展不确定的大背景下,集成电路行业的发展更离不开跨企业、跨领域的紧密合作。

20年来,思尔芯致力于构建一个良性的EDA产业生态,通过开放的平台,引导企业间建立合作机制,并通过产业间的良性竞争和产学研的合作推动整体发展。在EDA生态协作发展论坛暨思尔芯20周年成果展现场,思尔芯正式发布了《多元合作共创共赢行动计划》。

《多元合作共创共赢行动计划》是20年努力的延续,更是一种拓展。目前已经得到深圳国微芯科技有限公司、芯和半导体科技(上海)股份有限公司、武汉芯动科技有限公司、奇异摩尔(上海)集成电路有限公司、腾讯云计算(北京)有限责任公司等EDA、IP、设计公司、云服务等领域公司的响应,未来不将有更多的公司和高校加入。

在思尔芯20周年之际,希望依托这个行动计划,与合作伙伴共同加快创新步伐,深化生态合作,共赢共创更美好的未来。

思尔芯希望通过多元合作模式,能够更有效地应对市场挑战,确保下一个20年的精彩;同时也为合作伙伴和客户创造更多价值,共同推动技术创新和行业发展。