# AI/ML 处理器和应用程序的架构探索

#### 发布日期

2021年5月

# 目录

- 一、人工智能处理器架构探索简介

- 二、Google Tensor Processor 的架构探索示例

- 三、AI处理器的探索重点

- 四、人工智能系统示例-自动驾驶

- 五、结论

## 人工智能处理器架构探索简介

人工智能(AI)应用程序处理可以分布在处理器内的多核,PCIe 骨干网上的多个处理器板,分布在以太网网络中的计算机,高性能计算机或跨数据中心的系统中。AI 处理器具有巨大的内存大小要求,访问时间限制,在模拟和数字之间的分布以及硬件-软件分区。AI 处理器和系统的架构探索具有挑战性,因为它在硬件的功能上应用了数据密集型任务图,必须同时优化计算,存储,内存,管道,通信接口,软件和控制。

Genesis Architect 是可用于复杂计算系统(如 AI 处理器和系统)的架构设计软件。Genesis Architect 提供了一个平台,可以探索和权衡硬件和软件的体系结构,以创建一个经过全面验证的系统,满足项目截止日期和成本的考虑。

## Google Tensor Processor 的架构探索示例

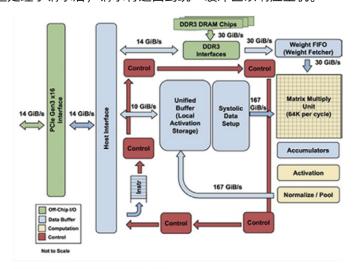

图一显示了 Google Tensor Processor 的内部视图。处理器通过 PCIe 接口接收来自主机的请求。运算所需的权重存储在片外 DDR3 中,并调入权重 FIFO。到达的请求在统一本地缓冲区中存储和更新,并发送给矩阵乘法单元进行处理。通过 AI 管道处理了请求后,请求将返回到统一缓冲区以响应主机。

TPU-1 block diagram. Source: Google.

图一:来自 Google 的 TPU-1

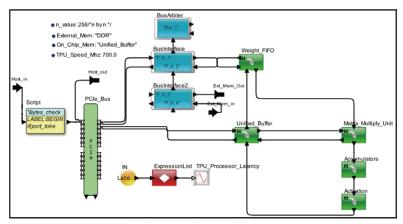

该框图已转换为图二中的架构模型。

图二:使用 Genesis Architect 设计的 AI 硬件架构模型

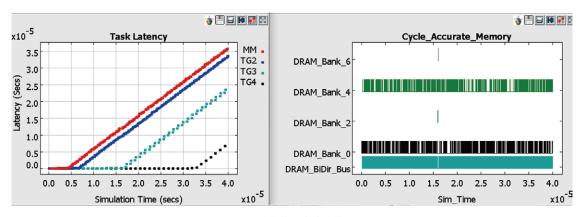

在图三中,您可以查看片外 DDR3 中的延迟和反向传播权重管理。延迟是从主机发送请求到接收响应的时间。 您将看到 TG3 和 TG4 能够保持低延迟,直到分别达到 200 us和 350 us。MM 和 TG2在仿真初期开始缓冲。这 表明 TPU 配置不足以处理到达的负载和所需的处理。TG3 和 TG4 的更高优先级已帮助其将运营维持了更长的时间。MM, TG2, TG3 和 TG4 是来自独立主机的不同请求流。

图三: 用于架构探索的统计数据

## AI 处理器的探索重点

AI 处理器和系统设计师使用应用程序类型,训练与推论,成本点,功耗和尺寸限制进行实验。例如,设计人员可以:

- 将子网络分配给流水线阶段

- 权衡深度神经网络(DNN)与常规机器学习算法之间的关系

- 在 GPU, TPU, AI 处理器, FPGA 和常规处理器上测量算法性能

- 评估融合计算和内存的好处

- 计算类似于人脑功能的模拟技术对电源的影响

- 使用针对单个应用程序的部分功能构建 SoC

在该示例中,架构探索的重点是内存访问。有许多选择: SRAM 与 DRAM,本地与分布式存储,内存中计算以及缓存反向传播系数与丢弃。

接着透过虚拟原型来探索总线或网络拓扑。虚拟原型可以具有用于处理器内部的片上网络,Tilelink 或 AMBA AXI 总线,用于连接多处理器板和机箱的 PCIe 或以太网,以及用于访问数据中心的 Wifi/5G/Internet 路由器。

最后分析是传感器,网络,数学运算,DMA,自定义逻辑,仲裁器,调度程序和控制功能的接口。

用例和流量模式适用于组装成硬件,RTOS 和网络的组合的架构模型。输入资讯流可以是周期性的,例如雷达,激光雷达和照相机,而用例可以是自动驾驶,聊天机器人,搜索,学习,推理,大数据操纵,图像识别和疾病检测。对于输入速率,数据大小,处理时间,优先级,相关性,先决条件,反向传播循环,系数,任务图和内存访问,用例和流量会有所不同。通过改变属性在系统模型上模拟用例,并生成各种统计信息和图表,包括高速缓存命中率,管线利用率,拒绝的请求数,每条指令或任务的瓦特数,吞吐量,缓冲区占用率和状态图。

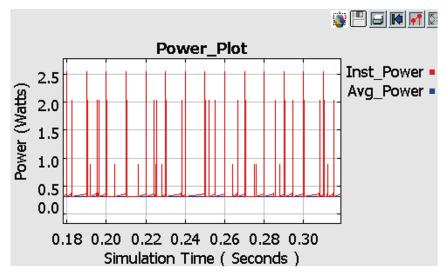

图四显示了系统或芯片的功耗。除了散热,电池电量消耗率和电池寿命周期变化外,该模型还可以捕获动态功率

#### 变化。

图四:实时测量 AI 处理器功耗

该模型绘制了每个设备的状态活动,相关的瞬时尖峰和系统的平均功率。尽早获得有关功耗的反馈,有助于热力和机械团队设计外壳和冷却方法。大多数机箱对每个板都有最大的功率限制。此早期功耗信息可用于在性能与性能之间进行权衡,从而寻找降低功耗的方法。

以下是一些其他 SoC 示例, 重点介绍了 AI 架构模型和分析的使用:

#### 1) 自动驾驶系统

- 将 360 度激光扫描仪,立体摄像机,鱼眼镜头,毫米波雷达,声纳和激光雷达连接到通过网关连接的多个 IEEE802.1Q 网络上的 20 个 ECU

- 该模型用于测试功能包的 OEM 硬件配置,以确定硬件和网络要求。主动安全措施的响应时间是主要标准

#### 2) 用于学习和推理任务的 AI 处理器

- 透过片上网路主干来设计,该主干构建有 32 个内核,32 个加速器,4 个 HBM2.0、8 个 DDR5,多个 DMA 和完整的缓存一致性

- 该模型在 RISC-V, ARM Z1 和专有内核上进行了试验。实现的目标是在链路上达到 40Gbps,同时保持 较低的路由器频率并重新训练网络路由

#### 3) 32 层深度神经网络

- 需要将内存从 40GB 减少到 7GB 以下,数据吞吐量和响应时间未更改

- 通过行为的功能流程图以及处理和反向传播的内存访问来设置模型

- 对于不同的数据大小和任务图,该模型确定了数据的丢弃量以及各种片外 DRAM 大小和 SSD 存储选项, 任务图随任意数量的图以及几个输入和输出而变化

#### 4) 使用 ARM 处理器和 AXI 总线进行低成本 AI 处理的通用 SoC

- 目标是获得最低的每瓦功率,从而最大化内存带宽。乘法累加功能被卸载到矢量指令,加密到 IP 内核, 定制算法到加速器

- 构建模型的明确目的是评估不同的缓存内存层次结构,以增加命中率和总线拓扑结构,以减少延迟

#### 5) 模数 AI 处理器

- 需要对功耗进行彻底分析,并对获得的吞吐量进行准确分析

- 在此模型中,非线性控制在离散事件模拟器中建模为一系列线性函数,以加快仿真速度

- 在这种情况下,对功能进行了测试,以检查行为并测量真正的节能效果

## 人工智能系统示例-自动驾驶

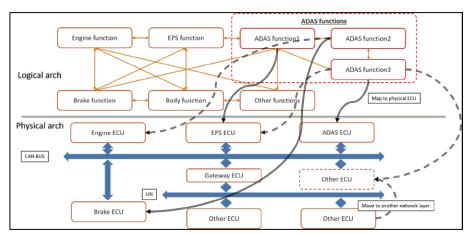

考虑自动驾驶应用程序,它是图五中 AI 部署的一种形式。ADAS 应用程序与计算机或电子控制单元(ECU)以及网络上的许多应用程序共存。为了使 ADAS 任务正确运行,还需要依赖这些现有系统的传感器和执行器。

图五:汽车设计中 AI 应用程序的逻辑到物理架构

早期的架构权衡可以测试和评估假设,以快速识别瓶颈,并优化规格以满足时序,吞吐量,功率和功能要求。在图五中,您将看到该架构模型需要硬件,网络,应用程序任务,传感器,衰减器和流量激励来获得整个系统运行的可见性。

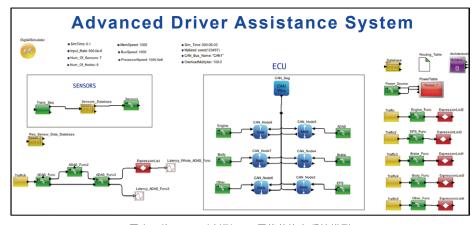

图六显示了此 ADAS 逻辑架构映射到物理架构的实现。使用架构模型的优点是能够分离设计的所有部分,从而可以研究单个操作的性能。您会注意到现有任务是单独列出的,具有 ECU,传感器生成和 ADAS 逻辑任务组织的 网络。ADAS 任务图中的每个功能都映射到 ECU。

图六:将 ADAS 映射到 ECU 网络的汽车系统模型

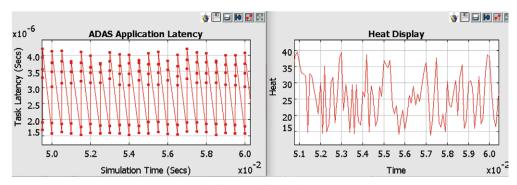

仿真 ADAS 模型后,您可以获得各种报告。在图七中,显示了完成 ADAS 任务的等待时间以及与此任务相关的

电池散热。其他感兴趣的图可以是测量的功率,网络吞吐量,电池消耗,CPU 利用率和缓冲区占用率。

图七:来自 ADAS 架构模型的分析报告

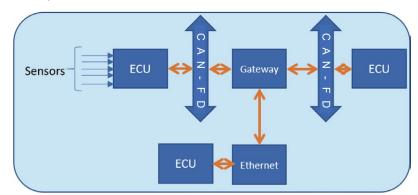

图八是包含 ECU, CAN-FD, 以太网和网关的网络框图。

图八: 具有 CAN 总线、传感器和 ECU 的汽车网络

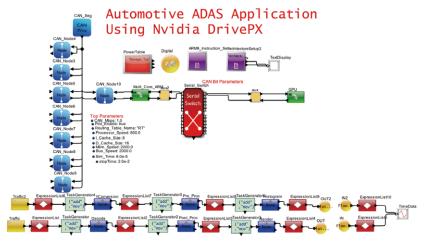

图九撷取了图八的一部分,该部分将 CAN-FD 网络与包含多个 ARM 内核和 GPU 的高性能 Nvidia DrivePX 集成在一起。从模型中删除了以太网/TSN/AVB 和网关,以简化视图。

图九: 自动驾驶和 E/E 架构的 Genesis Architect 模型

在此模型中,重点是了解 SoC 的内部行为。该应用程序是由车辆上的摄像头传感器触发的 MPEG 视频捕获,处理和渲染。图十显示了 AMBA 总线和 DDR3 内存的统计信息。您可以看到跨多个主服务器的工作负载分配。可以评估应用程序管道是否存在瓶颈,确定最高循环时间任务,内存使用情况配置内容以及每个任务的延迟。

```

DISPLAY AT TIME

----- 40.0000000 us -----

{AXI_Top_Master_1_Write_Data_Bytes

= 22272,

AXI_Top_Master_1_Write_Data_MBps

AXI_Top_Master_3_Read_Data_Bytes

AXI_Top_Master_3_Read_Data_MBps

556.8000000000001,

12224.

305.6,

AXI_Top_Master_5_Read_Data_Bytes

AXI_Top_Master_5_Read_Data_MBps

4928,

123.2,

AXI_Top_Master_7_Read_Data_Bytes

AXI_Top_Master_7_Read_Data_MBps

2496,

62.4.

AXI_Top_Slave_1_Read_Data_Bytes

19648,

AXI_Top_Slave_1_Read_Data_MBps

AXI_Top_Slave_1_Write_Data_Bytes

491.2,

21760

AXI_Top_Slave_1_Write_Data_MBps

544.0 }

"M_DDR_Mem_Ctrl",

{BLOCK

Total_Bytes

= 41344,

Total_Delay_Mean

Total_IOs_per_Second

= 1.7943237911025E-9,

= 6.4696452706518E7,

Total_MBs_per_Second

= 1035.14324330428 }

```

图十: 总线和内存活动报告

### 结论

Genesis Architect 的用户可以在带有大量模型库,以及 AI 硬件和软件建模组件的图形离散事件模拟平台中非常快速地构建架构模型。该模型可用于进行时序,吞吐量,功耗和服务质量的权衡。Genesis Architect 中可用的库支持模拟,内存,处理器,RTOS,加速器,乘法累加单元,DMA,网络接口,总线,网桥,FIFO,缓冲区,调度程序和仲裁方案。提供了 20 多个 AI 处理器和嵌入式系统模板(参考设计),以加速新 AI 应用程序的开发。为在 AI 系统中进行权衡而生成的报告包括响应时间,吞吐量,缓冲区占用率,平均功率,能耗和资源效率。

Genesis Architect 让研发团队在项目初期能迅速且确实做好架构规划,最终得以设计出低功耗、高效能的产品,是进行 AI/ML 产品开发的关键工具。

上海国微思尔芯技术股份有限公司

上海市浦东新区秀浦路2555号E1栋

www.s2ceda.com

© 2021 国微思尔芯保留所有权利。

S2C, Prototype Ready, ProtoBridge, Logic Matrix 和 Prodigy 是国微思尔芯的商标。